文主要讲解

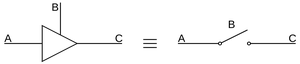

其模型为

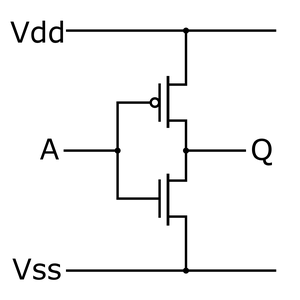

其实际电路为

其真值表为

BAC00Z01Z

:Z是高阻,不代表没有电压,而是电压不确定,受自身/旁边cell的影响

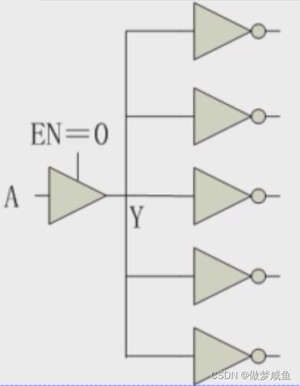

为什么三态门一般只能做在芯片的IO上,不能做在芯片内部?

回想起上一篇CMOS晶体管的延时中反相器的模型

答:在三态门为高阻态的情况下,若输出端口受到附近cell的影响使得输出端口C的电压在0.5Vdd附近,会使得其后连接的反相器中的NMOS和PMOS均处于持续导通状态,静态功耗急剧增大,严重时会烧毁电路,如下图所示。而三态门处于IO上时,一般外部电路会有上下拉电阻(如IIC),三态门的输出会被上拉到Vdd或者下拉到GND。

码字不易,欢迎点赞+关注+收藏

版权声明:

本文来源网络,所有图片文章版权属于原作者,如有侵权,联系删除。

本文网址:https://www.mushiming.com/mjsbk/5921.html