我们在上一章完成了UART串口通信的收发模块,这一章我们将FIFO引入进来,使用FIFO进行缓存数据,来连接串口通信的收发模块

FIFO即First In First Out,是一种先进先出数据存储、缓冲器,我们知道一般的存储器是用外部的读写地址来进行读写,而FIFO这种存储器的结构并不需要外部的读写地址而是通过自动的加一操作来控制读写,这也就决定了FIFO只能顺序的读写数据

同步FIFO

读和写应用同一个时钟。它的作用一般是做交互数据的一个缓冲,也就是说它的主要作用就是一个buffer。

异步FIFO

读写应用不同的时钟,它有两个主要的作用,一个是实现数据在不同时钟域进行传递,另一个作用就是实现不同数据宽度的数据接口。

同步FIFO和异步FIFO略有不同,下面的参数适用于两者。

,用参数FIFO_data_size表示,也就是FIFO存储的数据宽度;

,用参数FIFO_addr_size表示,也就是地址的大小,也就是说能存储多少个数据;

,full,当FIFO中的数据满了以后将不再能进行数据的写入;

,empty,当FIFO为空的时候将不能进行数据的读出;

,w_addr,由自动加一生成,将数据写入该地址;

,r_addr,由自动加一生成,将该地址上的数据读出;

同步FIFO和异步FIFO的最主要的不同就体现在空满标志产生的方式上,由此引出两者一些不同的参数。

同步FIFO

- 时钟,clk,rst,读写应用同一个时钟;

- 计数器,count,用计数器来进行空满标志的判断;

异步FIFO

- 时钟,clk_w,rst_w,clk_r,rst_r,读写应用不同的时钟;

- 指针,w_pointer_gray,r_pointer_gray,用指针来判断空满标识;

- 同步指针,w_pointer_gray_sync,r_pointer_gray_sync,指针的同步操作,用来做对比产生空满标志符;

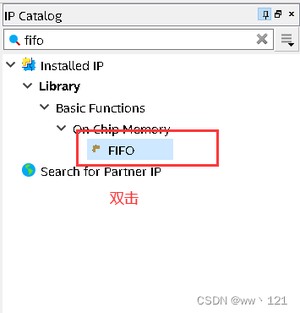

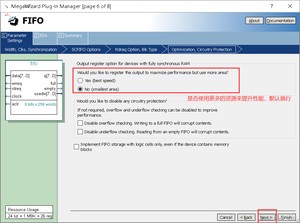

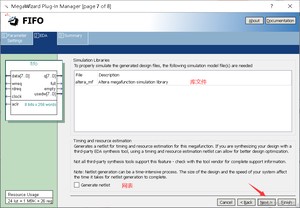

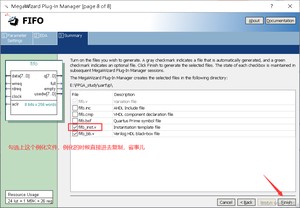

首先配置IP核

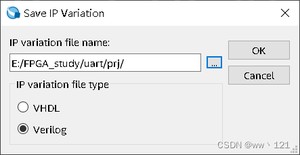

设置路径,我们一般会在工程目录下创建一个文件夹 ip 用来存放IP核文件

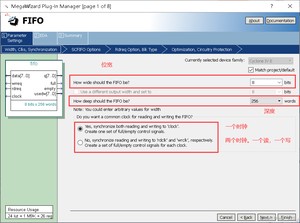

配置参数

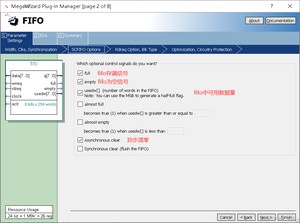

配置参数

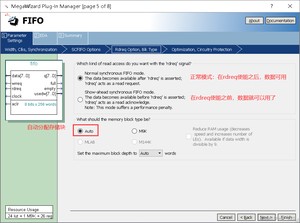

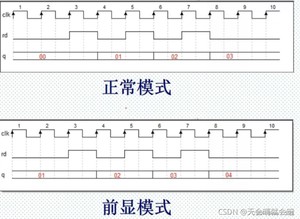

正常模式与前显模式:

区别:正常模式,输出数据与读请求信号差一个时钟周期;前显模式,将数据放于数据线上,在读请求信号拉高时,在下一个时钟周期,输出FIFO中的第二个数据。

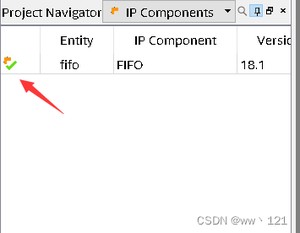

最后这样就成功引入FIFO了

调用ip核

testbench编写

写数据:

读数据:

思路:

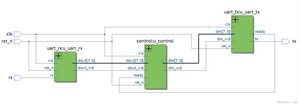

首先我们将整个项目分为4个模块

接收模块- - -从上位机接收数据,然后将数据发送给control模块

发送模块- - -从control模块接收数据,然后发送给上位机

FIFO缓存模块- - -缓存uart_rx接收的数据并输出给uart_tx

顶层模块

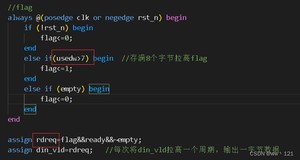

其中发送模块uart_tx增加了一个ready输出信号,因为发送模块每434个周期发送一位数据,为了防止FIFO不停的输出数据给发送模块,使用ready信号控制FIFO输出数据

由于只改动了发送模块和新增了control模块,这里只展示这两部分,源码见文章末尾

control:

uart_tx:

testbench:

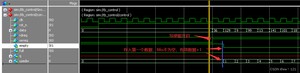

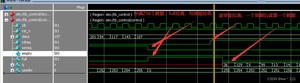

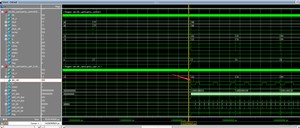

分析:

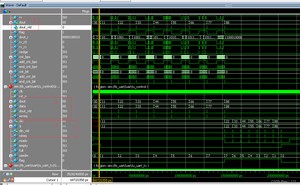

1.上位机发送数据到FPGA之后由FPGA的接收模块将和输出给

2.作为写使能信号,在写使能开启的时候存储

3.在FIFO中存储的数据的时候开启读使能,因为FIFO模式设置的前显模式,所以在读使能生效前,第一位数据就有效了,也就是时序图中的q信号:8’h11

然后来看发送数据:

箭头处,拉高一个周期,目的是为了在我们发送完一帧数据之前,只锁存一次数据,保证发送一帧数据期间数据不改变,将数据拼接起始位和停止位锁存到中

因为设置的FIFO存储满8个数据才开始读数据,所以这里看到发送8’h88之后才收到数据!!!

https://github.com/xuranww/uart_fifo.git

参考文章:

1.https://www.cnblogs.com/xuqing125/p/8337586.html

2.https://blog.csdn.net/QWERTYzxw/article/details/

版权声明:

本文来源网络,所有图片文章版权属于原作者,如有侵权,联系删除。

本文网址:https://www.mushiming.com/mjsbk/12507.html